您当前的位置:

科技成果 >

一种制备基于65nm工艺的冗余掺杂抗辐照MOS场效应管的方法

一种制备基于65nm工艺的冗余掺杂抗辐照MOS场效应管的方法

178

178 2018/08/31

2018/08/31

基本信息

-

成果类型

高等院校

-

委托机构

西安电子科技大学

-

成果持有方

西安电子科技大学

-

行业领域

电子元器件

-

项目名称

一种制备基于65nm工艺的冗余掺杂抗辐照MOS场效应管的方法

-

知识产权

发明专利

-

成果成熟度

-

项目简介

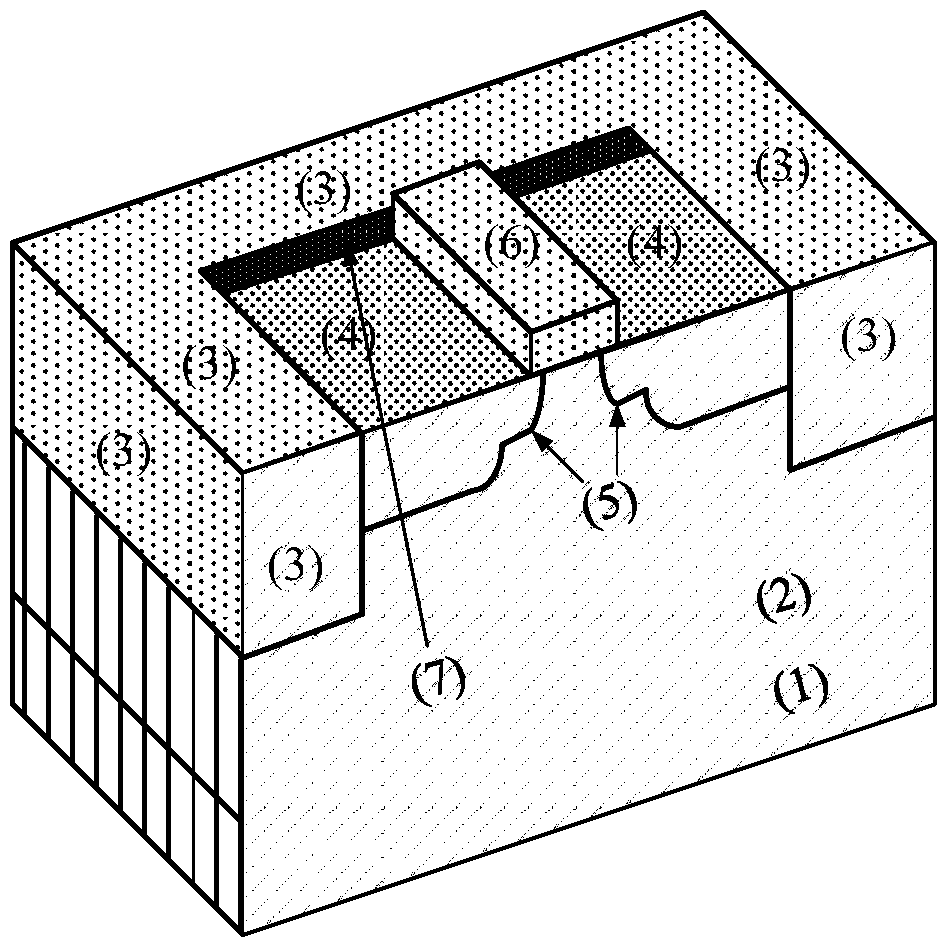

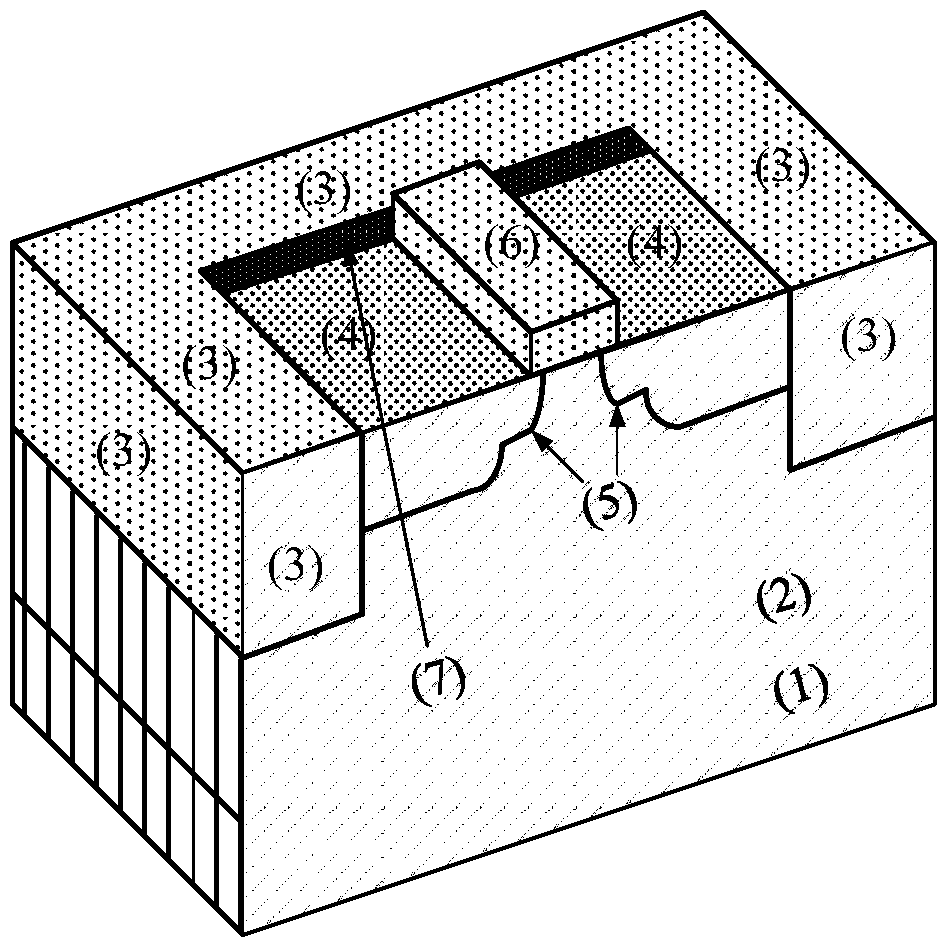

本发明公开了一种基于65nm工艺的冗余掺杂抗辐照MOS场效应管,主要解决传统65nm MOS场效应管在总剂量辐照环境下,阈值电压漂移、亚阈值摆幅退化和关态漏电流退化的问题。其包括P型衬底(1)和位于衬底上的外延层(2),外延层的上方四周和中部分别设有隔离槽(3)和栅极(6),栅极两侧边界到隔离槽内边界之间的外延层中设有源漏有源区(4),栅极两侧边界下方的外延层中设有轻掺杂源漏区(5),栅极正下方位于两个轻掺杂源漏区之间的区域形成沟道,在与沟道长度方向平行的两个侧边隔离槽底部,即该处的外延层界面上插有冗余掺杂区(7)。本发明提高了器件抗总剂量辐照能力,可用于大规模集成电路的制备。

-

交易信息

-

意向交易额

面议

-

挂牌时间

2017/11/21

-

委托机构

西安电子科技大学

-

分享至:

178

178 2018/08/31

2018/08/31 咨询成果

咨询成果 发布成果

发布成果