您当前的位置:

科技成果 >

垂直层叠应变Si/SiGe异质结CMOS器件结构及其制备方法

垂直层叠应变Si/SiGe异质结CMOS器件结构及其制备方法

316

316 2018/08/10

2018/08/10

基本信息

-

成果类型

高等院校

-

委托机构

西安电子科技大学

-

成果持有方

西安电子科技大学

-

行业领域

电子元器件

-

项目名称

垂直层叠应变Si/SiGe异质结CMOS器件结构及其制备方法

-

知识产权

发明专利

-

成果成熟度

-

项目简介

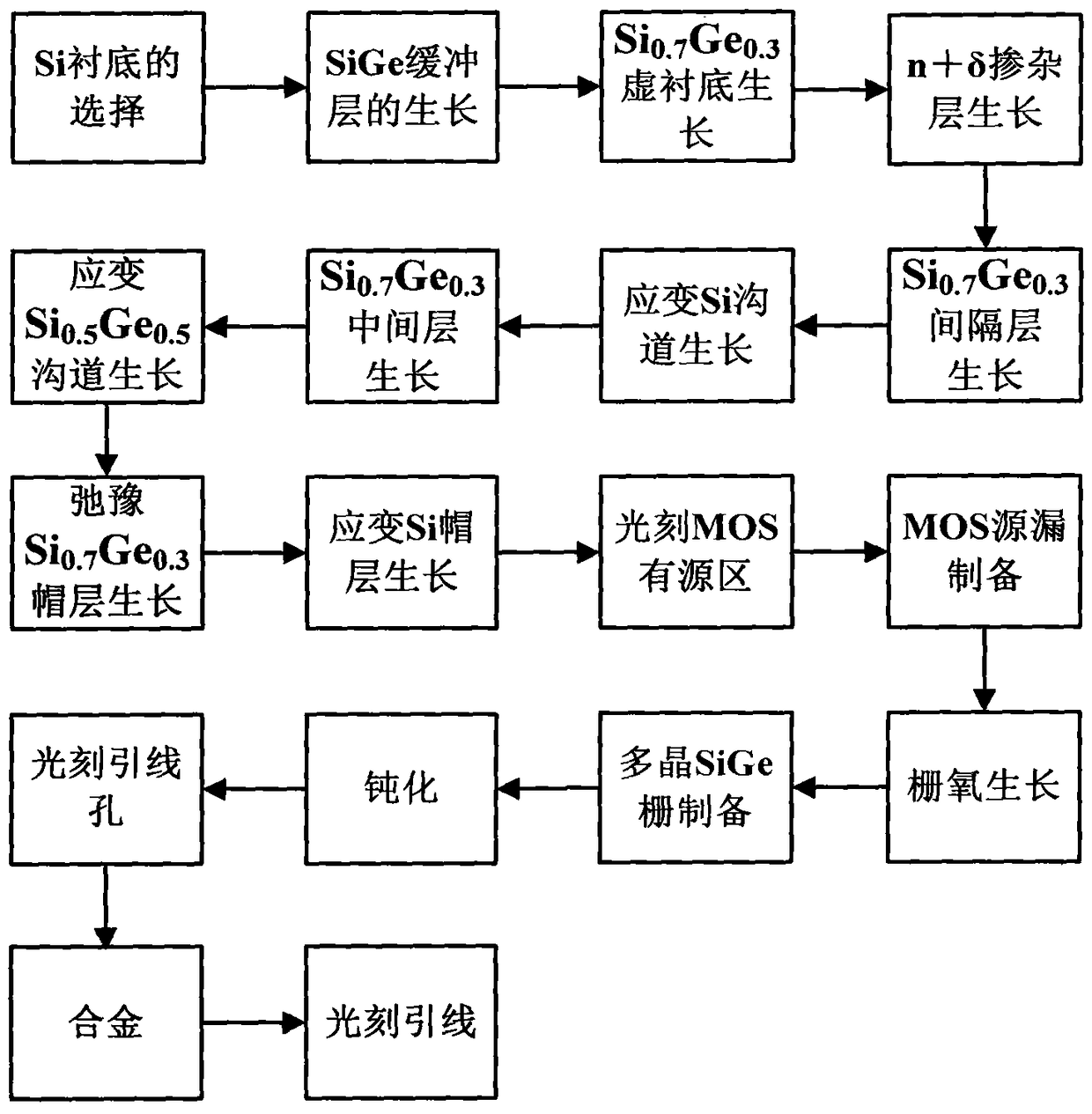

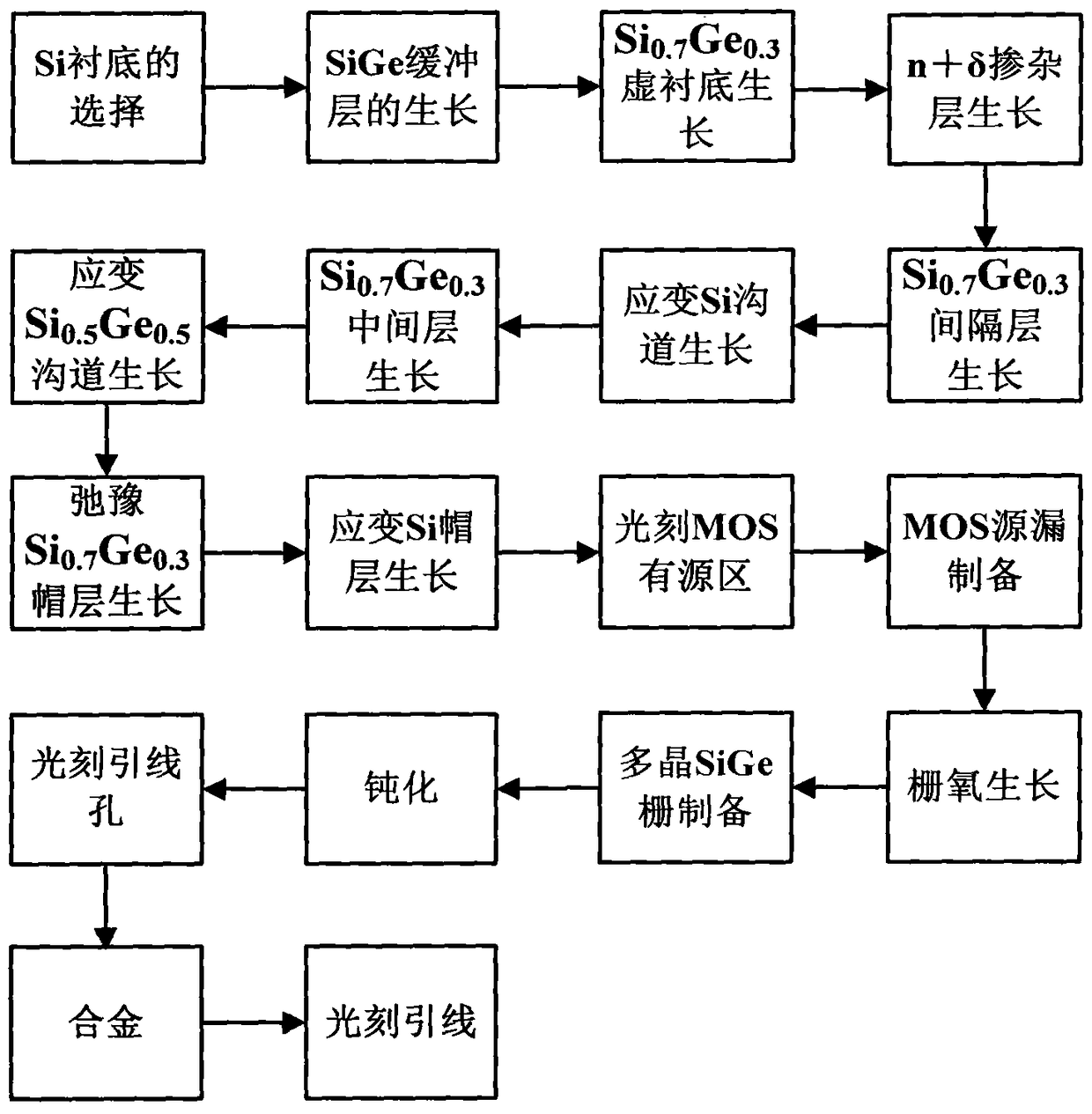

本发明公开了一种垂直层叠应变Si/SiGe异质结CMOS器件结构及其制备方法,该器件从下往上依次包括硅衬底、弛豫SiGe缓冲层、弛豫Si0.7Ge0.3虚衬底、n+δ掺杂层、弛豫Si0.7Ge0.3间隔层、应变Si沟道、弛豫Si0.7Ge0.3中间层、应变Si0.5Ge0.5沟道、弛豫Si0.7Ge0.3帽层和应变Si帽层。本发明采用张应变Si材料作n‑MOSFET沟道,压应变SiGe材料作p‑MOSFET沟道,n‑MOSFET与p‑MOSFET采用垂直层叠结构,二者共用一个多晶SiGe栅电极,电子和空穴的迁移率均有较大提高,提高了芯片的集成度、速度,为Si基器件和集成电路的高速、高频化发展开辟新的技术途径。

-

交易信息

-

意向交易额

面议

-

挂牌时间

2018/03/16

-

委托机构

西安电子科技大学

-

分享至:

316

316 2018/08/10

2018/08/10 咨询成果

咨询成果 发布成果

发布成果